Ҫ�����оƬ, ����, ��û�����һ�����������������Foundry (����ľ�Բ���칫˾)

����(�˴������а�Ȩ����… �Ͼ���Ҳ���ñ���Ǯ�ɻ�Ŀ��phd… �Ͳ���ȫ��·ͼ��… ��ҿ����ͺã� �����⣡��

����

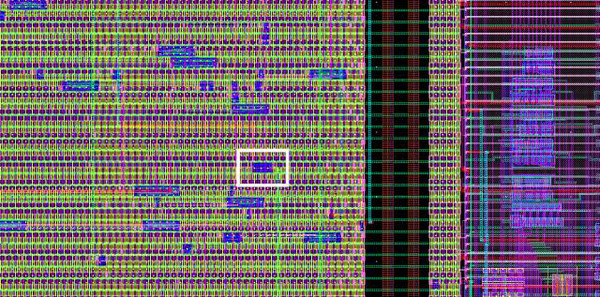

�����ٷŴ�...

����

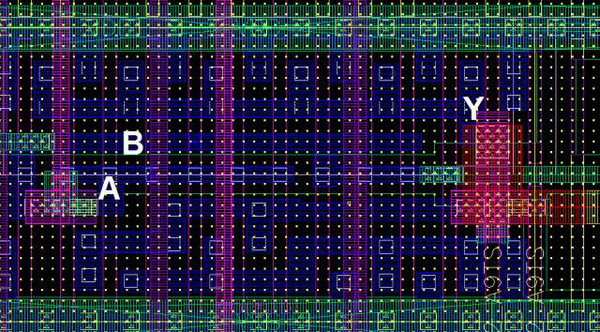

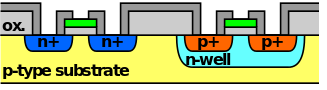

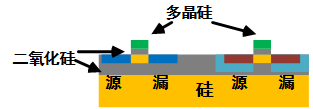

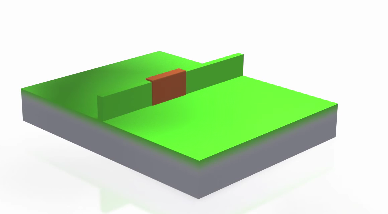

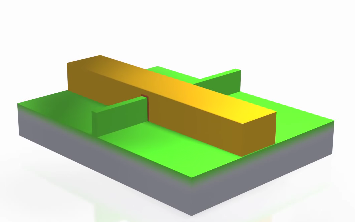

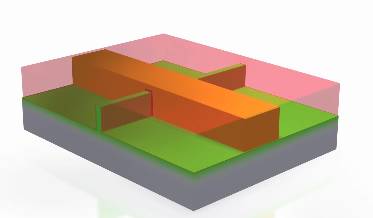

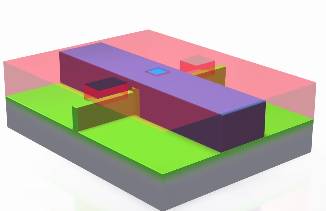

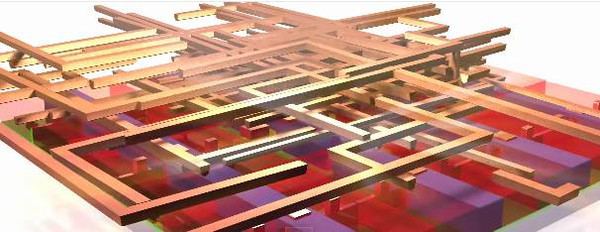

�����������ڿ���һ���ŵ�·��! ����һ��NAND Gate(�����), ���������:

����

����A, B ������, Y�����.

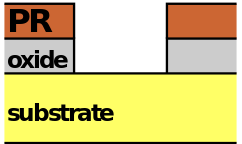

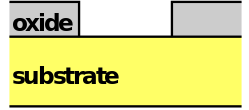

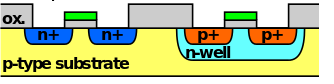

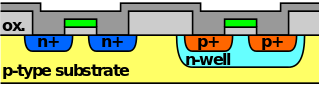

����������ɫ���ǽ���1��, ��ɫ�ǽ���2��, ��ɫ�ǽ���3��, ��ɫ�ǽ���4��...

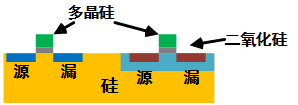

�����Ǿ����(����, ������"�����" ��199X���Ժ��Ѿ���Ҫ�� MOSFET, ����ЧӦ���� ) ��?

������ϸ��ͼ, ����������Щ��ɫ�ĵ���? ���dzĵ�, ����һЩ��ɫ�ı߿�? ��Щ��Active Layer (Ҳ�����Ӳ�.)

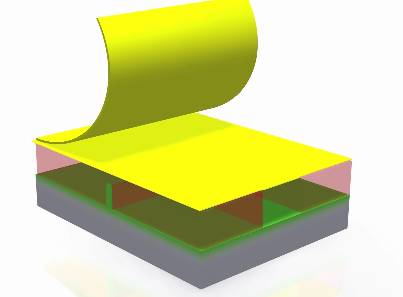

����Ȼ��Foundry����ô������? �����Ϸ�Ϊ���¼���:

�������ȸ㵽һ��ԲԲ�Ĺ辧Բ, (����һ��龧���, ��ĥ�ĺܹ⻬, һ����Բ��)

����ͼƬ����������������. ���Dz����ܽᵥ��д��.

����1��ʪϴ(�ø����Լ����ֹ辧Բ����û������)

����2����� (�����������ɰ�����辧Բ, ���յ��ĵط��ͻ����ױ�ϴ��, û���յ��ĵط��ͱ���ԭ��. ���ǾͿ����ڹ辧Բ����̳���Ҫ��ͼ��. ע��, ��ʱ��û�м�������, ��Ȼ��һ���辧Բ. )

����3�� ����ע��(�ڹ辧Բ��ͬ��λ�ü��벻ͬ������, ��ͬ���ʸ���Ũ��/λ�õIJ�ͬ������˳�ЧӦ��.)

����4.1����ʴ�� (֮ǰ�ù�̳�������״��������ʵ����������Ҫ��,����Ϊ������ע���ʴ�̵�. ���ھ�Ҫ�õ������������ϴ��, ������һЩ��һ������Ȳ���Ҫ�̳����Ľṹ, ��һ������ʴ��).

����4.2��ʪʴ��(��һ��ϴ��, �����õ����Լ�, ���Խ�ʪʴ��).--- ���ϲ�����ɺ�, ��ЧӦ�ܾ��Ѿ�����������~ �������ϲ���һ�㶼��ֹ��һ��, �ܿ�����Ҫ������������, �ԴﵽҪ��. ---

����5�������ӳ�ϴ(�ý����ĵ��������������оƬ)

����6���ȴ���, �����ַ�Ϊ:

����6.1���������˻� (����˲�������Ƭ��ͨ�����ʵ�ɶ���յ�1200���϶�����, Ȼ����������ȴ����, Ϊ��ʹ��ע��������ܸ��õı������Լ�������)

����6.2���˻�

����6.3�������� (�������������, Ҳ����ЧӦ�ܵ�դ��(gate) )

����7����ѧ�������(CVD), ��һ����ϸ��������ĸ�������

����8������������� (PVD),����, ���ҿ��Ը����в�����coating

����9������������ (MBE) �����Ҫ�������Ļ�����Ҫ���..

����10����ƴ���

����11����ѧ/��е ���洦��Ȼ��оƬ�Ͳ����, ��������Ҫ:

����12����Բ����

����13����Բ��ĥ�Ϳ��Գ�����װ��.������һ������:

�����Ϳ��Գ�����װ��.������һ������:

����

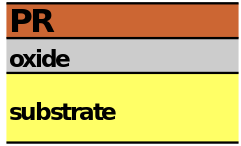

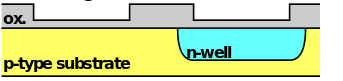

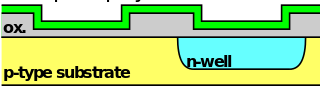

����1��������������, �����dzĵ�(��) -- ʪϴ

����

����2��һ����˵, �ȶ������ĵ�ע������(10^10 ~ 10^13 / cm^3) ��P������(�������һ������), ��Ϊ�ĵ� -- ����ע��

����

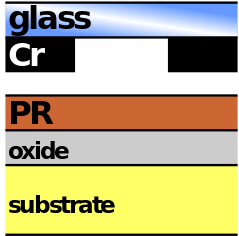

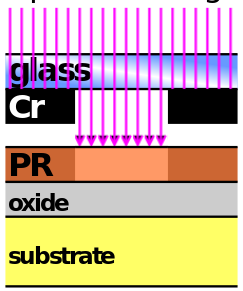

����3���ȼ���Photo-resist, ����ס���뱻ʴ�̵ĵط� -- ���

����

����4������Ĥ! (�����Ǹ���עCr�ĵط�. �м�յı�ʾû���ڸ�, �ڵı�ʾ��ס��.) -- ���

����

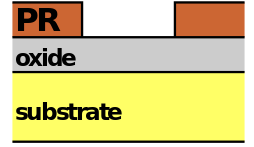

����5������������ȥ... ���汻�յ���һ��ͱ���Ӧ�� -- ���

����

����6����ȥ��Ĥ. -- ���

����

����7���ѱ�¶������������ϴ��, ¶�����(�Ϳ���ע��������) -- ���

����

����8���ѱ����㳷ȥ. �����͵õ���һ����ע��Ĺ�Ƭ. ��һ���ᷴ���ڹ�Ƭ�Ͻ���(��ʮ�������ϰٴ�). -- ���

����

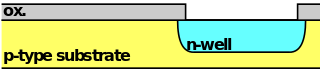

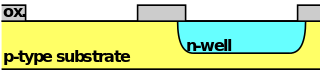

����9��Ȼ������Ϻ�, ������ݺݵز���һ������(10^14 ~ 10^16 /cm^3) ע���N�����ʾ�������һ��N-well (N-��) -- ����ע��

����

����10���ø�ʴ�̰���ҪP-well�ĵط�Ҳʴ�̳���. Ҳ�����ٴ�ʹ�ù�̳̿���. -- ��ʴ��

����

����11����ͼ��P-�Ͱ뵼���ϲ��ٴ�������һ�㱡���Ķ�������. -- �ȴ���

����

����12���÷��������Ӵ���������һ��ྦྷ�裬 �ò�ɵ��� -- ����������

����

����13����һ����ʴ��, ������ϸ�Ľṹ. (���˻��Լ�����CVD) -- �ظ�3-8��� + ʪʴ��13 ��һ����ʴ��, ������ϸ�Ľṹ. (���˻��Լ�����CVD) -- �ظ�3-8��� + ʪʴ��

����

����14���ٴκݺݵز������(10^18 ~ 10^20 / cm^3) ע���P/N������, ��ʱע��MOSFET�Ѿ���������. -- ����ע��

����

����15����������� �γɵĵ������ -- ��ѧ�������

����

����16����������ʴ�̳����� -- ��� + ʪʴ��

����

����17����������������� ������ -- �����������

����

����18�������������ʴ��. ��� + ʪʴ���ظ� 17-18 ����ÿ��������Ŷ����... �ʼ�Ǹ�оƬ, ��С��Լ��1.5mm x 0.8mm

������~~ �ҵ�һ�����ڹ�̵���, ����һ��, ֮ǰ�Ļش�������..

��������: << IC Fabrication Technology >> By BOSE

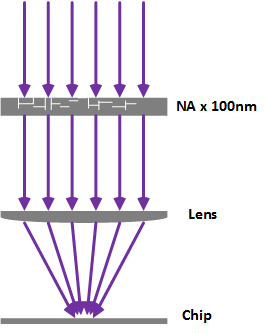

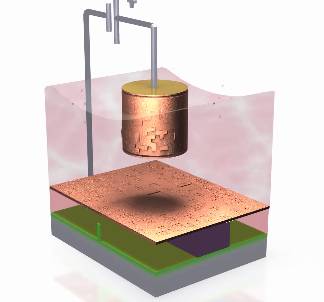

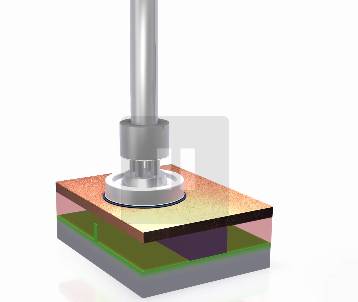

����ϸ˵һ�¹��. ��������: С��ͷ��˿ֱ���IJ����������, ���Թ��(����˵100nm)����ô������?

��������˵����Ҫ��һ��100nm���ŵ�·(90nm technology), ��ôʵ������������:

����

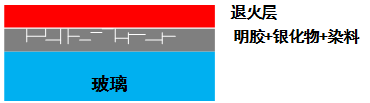

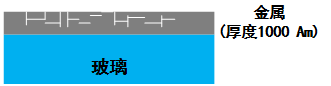

���������Ĥ�ǵ�һ��, �����10�����ҵ�Die Size�����ַ�������: Emulsion Mask �� Metal MaskEmulsion Mask:

����

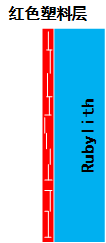

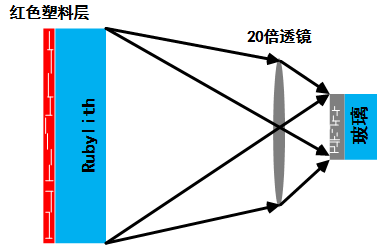

��������ֱ��ʿ��Դﵽ 2000line / mm (��ʵͦ���... ����sub-micron ,Ҳ��um�������µ� VLSI����... )����ֱ��ʿ��Դﵽ 2000line / mm (��ʵͦ���... ����sub-micron ,Ҳ��um�������µ� VLSI����... )��������: ����: ��Ҫ��Rubylith (���ᷭ��...) ����̳�һ������Ҫ����Ĥ���20������״ (��������������ߴ��200��), �����״�Ϳ����ü���ʲô�Ŀ̳���, ֻ��Ҫ����Ŀ̶�.

����

����Ȼ��:

����

������!��!��!��! , ��Ƭ����Emulsion Mask! ��!��!��!��! , ��Ƭ����Emulsion Mask! ���Ҫ�ĵ�"��Ƭ"̫��, Ҳ�з������յķ���. Metal Mask:

����

������������: 1������һ��Emulsion Mask, Ȼ����Emulsion Mask�Լ���֮ǰ�ᵽ��17-18����Metal Mask! ˲������Recursion�ĸо���ľ��!!!

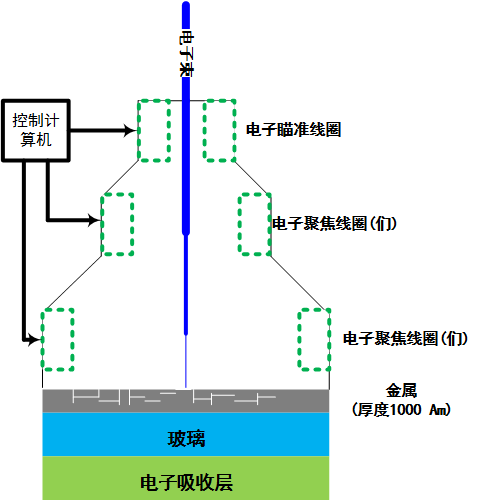

����2��Electron beam:

������ų�����

����

����������ʱ���ƶ����ǵ����Dz�. ���������ƶ�.

���������ӡ��һ���ѵ��´�һ��.

�����ô��Ǿ����ر��, Ŀǰ������߾��ȵ�(<100nm����)���������Ĥ. ������̫��...

����������Ĥ��:

����Feature Size = k*lamda / NA

����kһ����0.4, �����������й�; lamda�����ù�IJ���; NA�Ǵ�оƬ����ȥ, �Ŵı���.

������Ŀǰ�ļ���ˮƽ, �����ʽ�Ѿ�����, ��Ϊ����Feature Size��С, ���ĺ��Ҳ��һ��������

����Feature Size = k * lamda / NA^2

������.. ������ʵ��Ĥ�������ı�оƬ��һЩ. ���ھ�����������, һ�����ø߾��ȼ����̽�� + ����ֱ�ӿ̰�. Photomask(��Ĥ) �IJ���ѡ��һ��Ҳ�ȹ辧Ƭ�������, ���Բ��ú����ױ����������IJ��Ͻ�������.

���������̵ķ��������Ǹ��ڿƼ�һ��ĵ�! ֱ�Ӱ�Lamda��С��һ������, With no extra cost! ����˵��!

����Food for Thought: Wikipedia���������Ĥ�İ������������һ��ͼ, ��������������Ĥ�������������ʲô��״��?

����

�������ǻ�û������Food for thought...

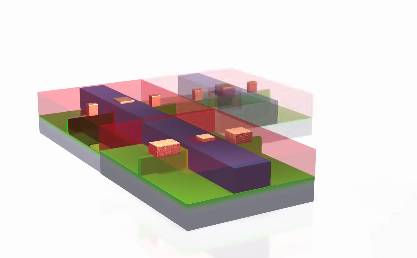

������ͼ�IJ�����ÿ��ͼ�������ע, һ��18��.

�������ճ��ʹ�ų�����:

����

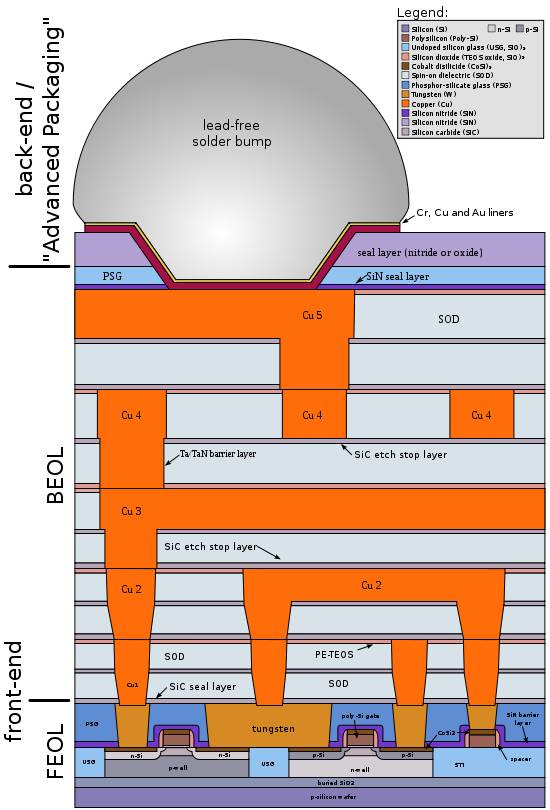

��������, ����1-15 ���� ǰ�˴��� (FEOL), Ҳ�����������ЧӦ��

��������16-18 (�������������ظ�) ���ں�˴��� (BEOL) , ��˴�����Ҫ����������. �ʼ�Ǹ���оƬ�����ܿ����Ļ������Dz���! һ��һ���߶ȼ��е�оƬ�ϼ����������ײ�Ĺ�Ƭ, ���ᱻ�����ڵ�ס.

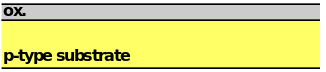

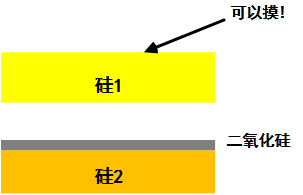

����SOI (Silicon-on-Insulator) ����:

������ͳCMOS������ȱ������: �ĵĺ�Ȼ�Ӱ��Ƭ�ϵļ�������, ��ӵ���оƬ�������½�. SOI������Ҫ�ǽ� Դ��/©�� �� ��Ƭ�ĵֿ�, �Դﵽ(����)�����������ݵ�Ŀ��.

������ͳ:

����

����SOI:

����

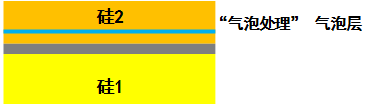

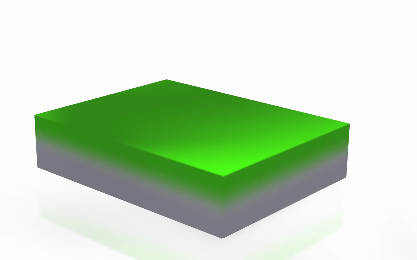

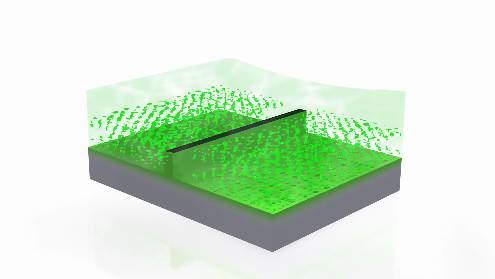

��������������Ҫ�����¼���(��Ҫ����������-��������-��Ľṹ, ֮��IJ������ͳ���ջ���һ��.)1. ���������˻�:

����

�����ڹ��������ע��һ�������Ӳ�

������������������, �γɸ�����

����

���������˻�

��������.

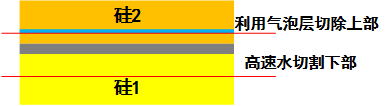

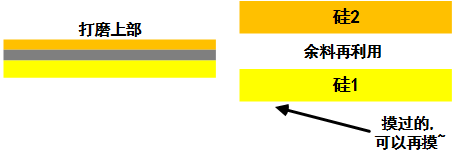

����������2. Wafer Bonding(������! )����Ҫ�����ı���һ���Ľṹ��? ү����Ǯ! ������!

����

����������!

����

�����Թ�2���б�������

����

�����Թ�2����������ע��Թ�2����������ע��

����

��������

����

�����������Ӳ㴦�������ݲ㽫�����Ӳ㴦�������ݲ�

����

�����и�����ಿ���и�����ಿ��

����

��������! + ������

����

�������

����

��������ע������ע��

����

������ͼ������:

����

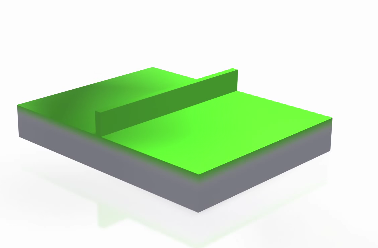

�����ٴι��+ʴ��

����

������ȥ����, �м��Ǹ�����Fin��ȥ����, �м��Ǹ�����Fin

����

�����Ų�λ�Ķྦྷ��/��K���������Ų�λ�Ķྦྷ��/��K��������

����

�����Ų�λ�������������Ų�λ������������

����

������������

����

����Դ�� ©������(���+ ����ע��)

����

�����������/�ྦྷ����Ƭ

����

����ʴ��+����

����

����������������������������(��Ϊ����ά�ṹ, ��������Ҫ���ϲ�����)

����

������е��ĥ(��! ����ĥ�ᵼ�½������Ȳ�һ��)

����

��������! ����!

����

��������

������ž��ǽ���...

��ࣺ����֪ʶ��